## **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (Po), Coimbatore – 641 107

#### An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

## Sub: Microcontroller Programming And Interfacing Subcode:23ECB202 Unit-I

PIC Microcontrollers: History, Features, & Architecture 16F877a or16F8XX Registers File Structure

## **The Registers**

A register is a place inside the PIC that can be written to, read from or both. Think of a register as a piece of paper where you can look at and write information on.

## **Register File Structure**

- Register file → locations that an instruction can access via an address.

- Register file consists of two component:-

- 1. General purpose register file (same as RAM)

- 2. Special purpose register file

#### 128 bytes

# W or Working Register

- 8 bits wide

- Contains one of the source operands during the execution of instructions.

- Serve as the destination for the result of the operation.

- Only used for ALU operations..

#### **Status Register (8 bits)**

|        |       |       |       |       |       | R/W (x) |       |       | Features |

|--------|-------|-------|-------|-------|-------|---------|-------|-------|----------|

| STATUS | IRP   | RP1   | RP0   | то    | PD    | Z       | DC    | С     | Bit name |

|        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0 |          |

| IRP - Bit selects register bank. It is used for indirect addressing.                                                                                                                     | <ul> <li>1 - Banks 0 and 1 are active (memory location 00h-FFh)</li> <li>0 - Banks 2 and 3 are active (memory location 100h-1FFh)</li> </ul>                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RP1,RP0                                                                                                                                                                                  | • Bits select register bank. They are used for direct addressing.                                                                                                                                                                                      |

| TO - Time-out bit.                                                                                                                                                                       | <ul> <li>1 - After power-on or after executing CLRWDT instruction which resets watch-dog timer<br/>or SLEEP instruction which sets the microcontroller into low-consumption mode.</li> <li>0 - After watch-dog timer time-out has occurred.</li> </ul> |

| PD - Power-down bit.                                                                                                                                                                     | <ul> <li>1 - After power-on or after executing CLRWDT instruction which resets watch-dog timer.</li> <li>0 - After executing SLEEP instruction which sets the microcontroller into low-<br/>consumption mode.</li> </ul>                               |

| Z - Zero bit                                                                                                                                                                             | <ul> <li>1 - The result of an arithmetic or logic operation is zero.</li> <li>0 - The result of an arithmetic or logic operation is different from zero.</li> </ul>                                                                                    |

| DC - Digit carry/borrow bit is changed during<br>addition and subtraction if an "overflow" or a<br>"borrow" of the result occurs.<br>C - Carry/Borrow bit is changed during addition and | <ul> <li>1 - A carry-out from the 4th low-order bit of the result has occurred.</li> <li>0 - No carry-out from the 4th low-order bit of the result has occurred.</li> </ul>                                                                            |

| subtraction if an "overflow" or a "borrow" of the<br>result occurs, i.e. if the result is greater than 255 or<br>less than 0.                                                            | <ul> <li>1 - A carry-out from the most significant bit of the result has occurred.</li> <li>0 - No carry-out from the most significant bit of the result has occurred.</li> </ul>                                                                      |

23ECB202/ PIC16F877A Registers/ Dr. Husna/ ECE/SNSCE

- Microchip has provided only direct addressing mode for the register file with 7-bits address plus remaining 8th and 9th bits frozen in the STATUS REGISTER bits RP1:RP0.

- 11 = Bank 3 (180h-1FFh)

- 10 = Bank 2 (100h-17Fh)

- 01 = Bank 1 (80h-FFh)

- 00 = Bank 0 (00h-7Fh)

- As shown in figure

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

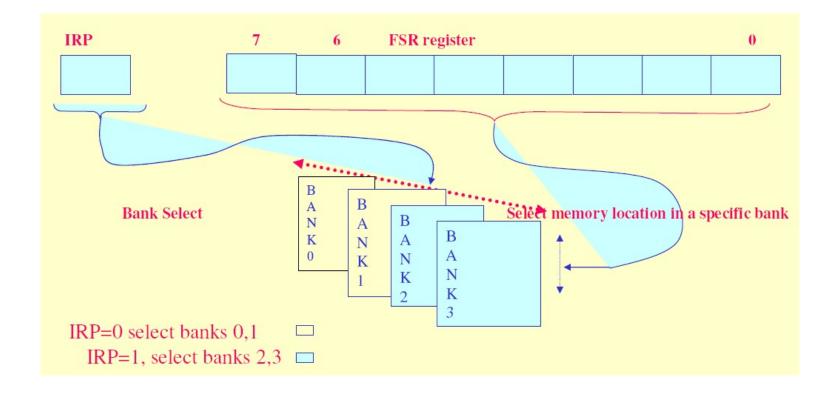

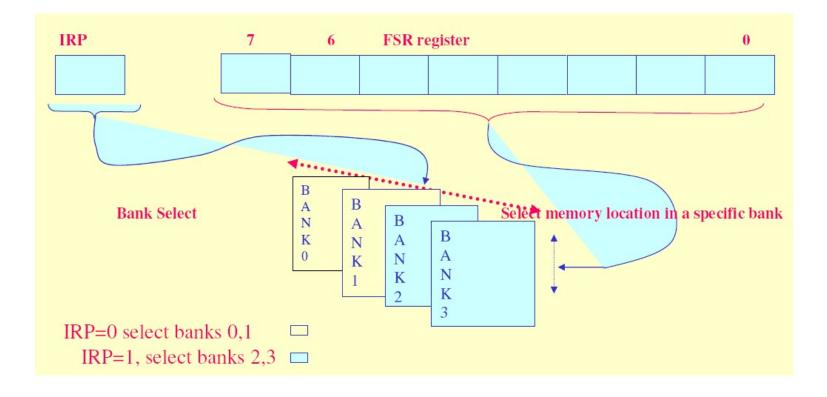

#### Use of IPR bit in indirect addressing mode

#### Indirect addressing mode

- IRP bit is used for indirect addressing.

- The IRP bit allows selecting either

- 1= Bank 2 & bank 3

- 0= Bank 0 & bank 1

- The IPR bit and FSR decide the effective 9 bit address. As shown in figure

### Use of IPR bit in indirect addressing mode

## **Special Function Register**

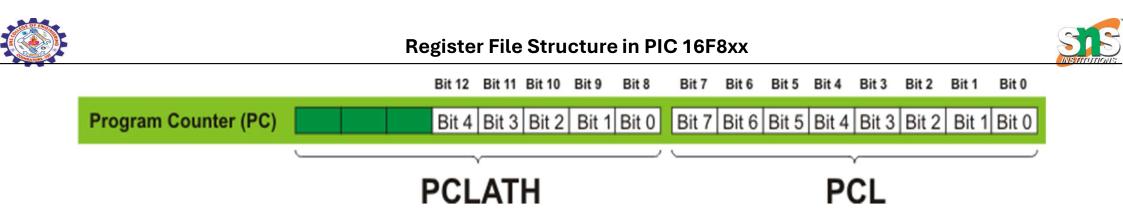

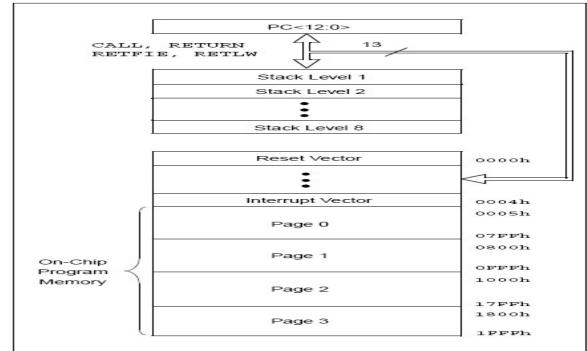

PCL and PCLATH Registers: The size of the program memory of the PIC16F887 is 8K. Therefore, it has 8192 locations for program storing. For this reason the program counter must be 13-bits wide (2^13 = 8192). In order that the contents of some location may be changed in software during operation, its address must be accessible through some SFR. Since all SFRs are 8-bits wide, this register is "artificially" created by dividing its 13 bits into two independent registers: PCLATH and PCL.

- Eight lower bits (the low byte) come from the PCL register which is readable and writable, whereas five upper bits coming from the PCLATH register are writable only.

- The PCLATH register is cleared on any reset.

#### PCL

- Program Counter byte.

- PCL is the lower byte of the PC.

- Cause PCLATH contents to be transferred to the PC higher bit locations.

- PC of PIC is associated with an 8-level stack.

- PC always points to the next instruction to be executed.

- In case of call to subroutines, the returned address is pushed onto the stack.

- After the return from called subroutine, this return address is retrieved.

- Stack width and PC width should be same.

#### **Power control register**

- Contains the flags which can differentiate between the type of reset occurred namely

- $\circ$  Power on reset

- o Brown out reset

|  |  | POR | BOR |  |

|--|--|-----|-----|--|

|--|--|-----|-----|--|

#### Stack

- The entire PIC chip has an area for storing the return addresses.

- This area or unit called Stack is used in some Peripheral interface controllers.

### PIC16F87XA Data Memory Organization

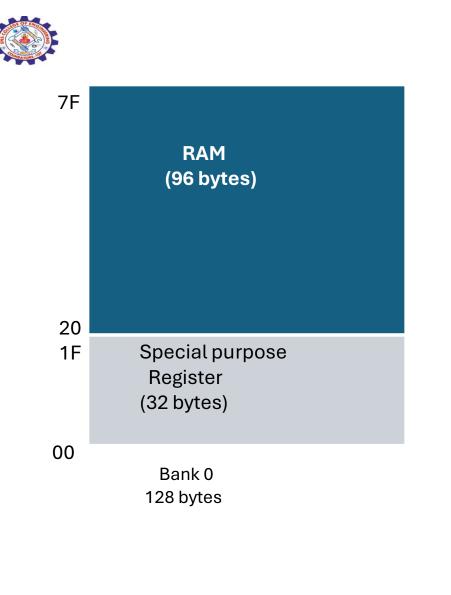

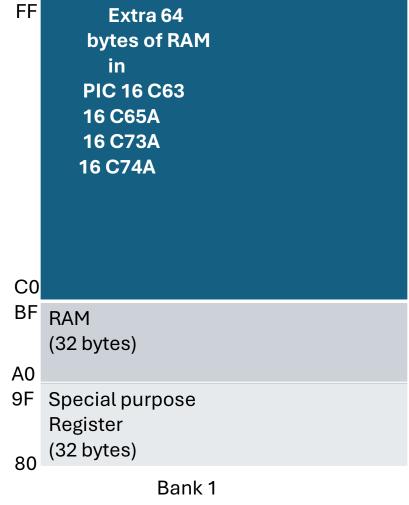

- Data memory is divided in two four banks, Each bank holds 128 bytes of addressable memory.

- Contain GPR and SPR.

- The banked arrangement is necessary because there are only 7 bits are available in the instruction word for the addressing of a register, which gives only 128 addresses.

- The selection of the banks are determined by control bits RP1, RP0 in the STATUS registers

- Together the RP1, RP0 and the specified 7 bits effectively form a 9 bit address.

#### Register File Structure in PIC 16F8xx

#### File Address

|                                            |     |                                            |     |                                            |      |                                            | duress       |

|--------------------------------------------|-----|--------------------------------------------|-----|--------------------------------------------|------|--------------------------------------------|--------------|

| Indirect addr.(*)                          | 00h | Indirect addr.(*)                          | 80h | Indirect addr.(*)                          | 100h | Indirect addr.(*)                          | 180h         |

| TMR0                                       | 01h | OPTION_REG                                 | 81h | TMR0                                       | 101h | OPTION_REG                                 | 181h         |

| PCL                                        | 02h | PCL                                        | 82h | PCL                                        | 102h | PCL                                        | 182h         |

| STATUS                                     | 03h | STATUS                                     | 83h | STATUS                                     | 103h | STATUS                                     | 183h         |

| FSR                                        | 04h | FSR                                        | 84h | FSR                                        | 104h | FSR                                        | 184h         |

| PORTA                                      | 05h | TRISA                                      | 85h |                                            | 105h |                                            | 185h         |

| PORTB                                      | 06h | TRISB                                      | 86h | PORTB                                      | 106h | TRISB                                      | 186h         |

| PORTC                                      | 07h | TRISC                                      | 87h |                                            | 107h |                                            | 187h         |

| PORTD (1)                                  | 08h | TRISD (1)                                  | 88h |                                            | 108h |                                            | 188h         |

| PORTE (1)                                  | 09h | TRISE (1)                                  | 89h |                                            | 109h |                                            | 189h         |

| PCLATH                                     | 0Ah | PCLATH                                     | 8Ah | PCLATH                                     | 10Ah | PCLATH                                     | 18Ah         |

| INTCON                                     | 0Bh | INTCON                                     | 8Bh | INTCON                                     | 10Bh | INTCON                                     | 18Bh         |

| PIR1                                       | 0Ch | PIE1                                       | 8Ch | EEDATA                                     | 10Ch | EECON1                                     | 18Ch         |

| PIR2                                       | 0Dh | PIE2                                       | 8Dh | EEADR                                      | 10Dh | EECON2                                     | 18Dh         |

| TMR1L                                      | 0Eh | PCON                                       | 8Eh | EEDATH                                     | 10Eh | Reserved <sup>(2)</sup>                    | 18Eh         |

| TMR1H                                      | 0Fh |                                            | 8Fh | EEADRH                                     | 10Fh | Reserved <sup>(2)</sup>                    | 18Fh         |

| T1CON                                      | 10h |                                            | 90h |                                            | 110h |                                            | 190h         |

| TMR2                                       | 11h | SSPCON2                                    | 91h |                                            | 111h |                                            | 191h         |

| T2CON                                      | 12h | PR2                                        | 92h |                                            | 112h |                                            | 192h         |

| SSPBUF                                     | 13h | SSPADD                                     | 93h |                                            | 113h |                                            | 193h         |

| SSPCON                                     | 14h | SSPSTAT                                    | 94h |                                            | 114h |                                            | 194h         |

| CCPR1L                                     | 15h |                                            | 95h |                                            | 115h |                                            | 195h         |

| CCPR1H                                     | 16h |                                            | 96h |                                            | 116h |                                            | 196h         |

| CCP1CON                                    | 17h |                                            | 97h | General<br>Purpose                         | 117h | General<br>Purpose                         | 197h         |

| RCSTA                                      | 18h | TXSTA                                      | 98h | Register                                   | 118h | Register                                   | 198h         |

| TXREG                                      | 19h | SPBRG                                      | 99h | 16 Bytes                                   | 119h | 16 Bytes                                   | 199h         |

| RCREG                                      | 1Ah |                                            | 9Ah |                                            | 11Ah |                                            | 19Ah         |

| CCPR2L                                     | 1Bh |                                            | 9Bh |                                            | 11Bh |                                            | 19Bh         |

| CCPR2H                                     | 1Ch |                                            | 9Ch |                                            | 11Ch |                                            | 19Ch         |

| CCP2CON                                    | 1Dh |                                            | 9Dh |                                            | 11Dh |                                            | 19Dh         |

| ADRESH                                     | 1Eh | ADRESL                                     | 9Eh |                                            | 11Eh |                                            | 19Eh         |

| ADCONO                                     | 1Fh | ADCON1                                     | 9Fh |                                            | 11Fh |                                            | 19Fh         |

|                                            | 20h |                                            | A0h |                                            | 120h |                                            | 1A0h         |

| General<br>Purpose<br>Register<br>96 Bytes |     | General<br>Purpose<br>Register<br>80 Bytes | EFh | General<br>Purpose<br>Register<br>80 Bytes | 16Fh | General<br>Purpose<br>Register<br>80 Bytes | 1EFh         |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,    | 7Fh | accesses<br>70h-7Fh                        | FOh | accesses<br>70h-7Fh                        | 170h | accesses<br>70h - 7Fh                      | 1F0h<br>1FFh |

| Bank 0                                     |     | Bank 1                                     |     | Bank 2                                     |      | Bank 3                                     |              |

# Thanks