### **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (PO), Coimbatore - 641 107 Accredited by NAAC-UGC with 'A' Grade Approved by AICTE, Recognized by UGC & Affiliated to Anna University, Chennai

**DEPARTMENT OF CSE (IoT) COURSE NAME: 23ITT201 DIGITAL PRINCIPLES AND COMPUTER ORGANIZATION II YEAR/ III SEM Unit 3 : COMPUTER FUNDAMENTALS Instruction and Instruction Sequencing**

23ITT201 / DP & CO / D.KAVITHA/AP/CSE(IoT) / Unit 3 / COMPUTER FUNDAMENTALS

10/19/2024

10/19

# "Must-Perform" Operations

- Data transfers between the memory and the processor lacksquareregisters

- Arithmetic and logic operations on data

- Program sequencing and control

- I/O transfers  $\bullet$

# **Register Transfer Notation**

- Identify a location by a symbolic name standing for its hardware binary address (LOC, R0, DATAIN, ...)

- Contents of a location are denoted by placing square brackets around the name of the location R1←[LOC] R3 ←[R1]+[R2]

- This type of notation is Register Transfer Notation (RTN)

23ITT201 / DP & CO / D.KAVITHA/AP/CSE(IoT) / Unit 3 / COMPUTER FUNDAMENTALS

- Assembly language(symbolic machine code) takes complete control over the system and its resources.

- Represent machine instructions and programs.

- Move LOC, R1

- Add R1, R2, R3

23ITT201 / DP & CO / D.KAVITHA/AP/CSE(IoT) / Unit 3 / COMPUTER FUNDAMENTALS

## Instruction Formats

- Three-Address Instructions

- Format: Operation Source1, Source2, Destination

- $\circ$  ADD R2, R3, R1 R1  $\leftarrow$  [R2] + [R3]

- Two-Address Instructions • Format: Operation Source, Destination o ADD R2, R1  $R1 \leftarrow [R1] + [R2]$

- One-Address Instructions

- o ADD M  $AC \leftarrow [AC] + [M]$

- $\circ$  Load A

- o Store A

23ITT201 / DP & CO / D.KAVITHA/AP/CSE(IoT) / Unit 3 / COMPUTER FUNDAMENTALS

10/19/2024

### **Instruction Formats**

Example: Evaluate C = A+B using processor registers,

| Move | А,               | R <sub>i</sub>   |

|------|------------------|------------------|

| Move | В,               | R <sub>i</sub>   |

| Add  | R <sub>i.</sub>  | , R <sub>i</sub> |

| Move | R <sub>j</sub> , | Ċ                |

23ITT201 / DP & CO / D.KAVITHA/AP/CSE(IoT) / Unit 3 / COMPUTER FUNDAMENTALS

10/19/2024

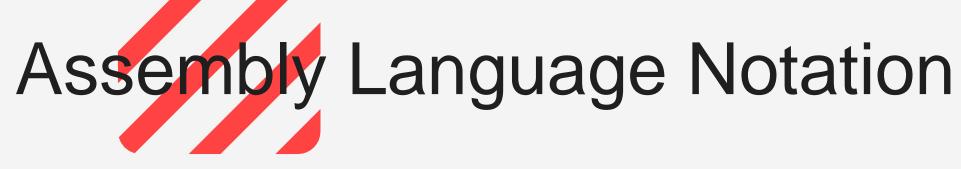

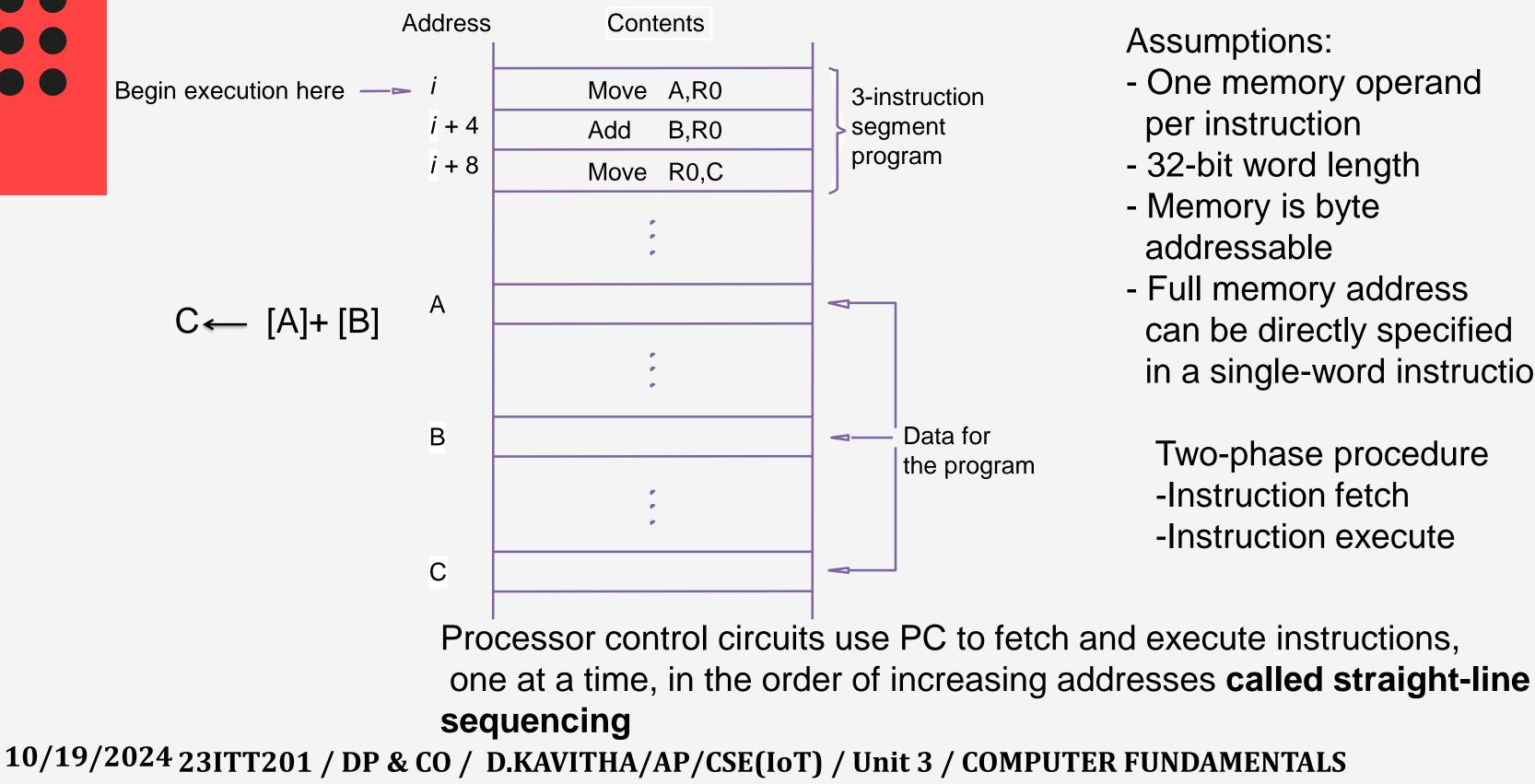

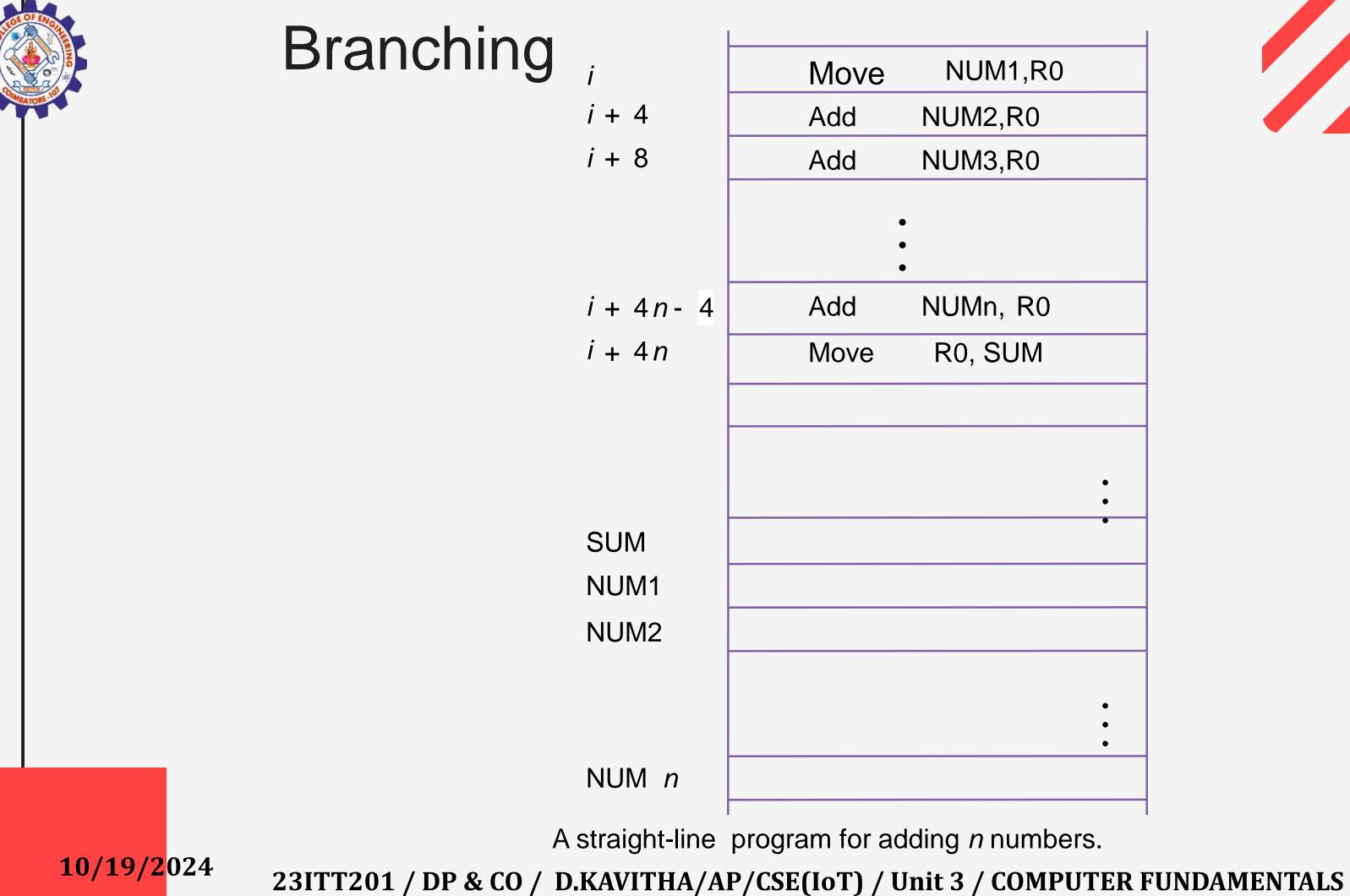

# Instruction Execution and Straight-Line Sequencing

Assumptions:

- One memory operand per instruction

- 32-bit word length

- Memory is byte addressable

- Full memory address can be directly specified in a single-word instruction

Two-phase procedure -Instruction fetch -Instruction execute

10/19/2024 23ITT201 / DP & CO / D.KAVITHA/AP/CSE(IoT) / Unit 3 / COMPUTER FUNDAMENTALS

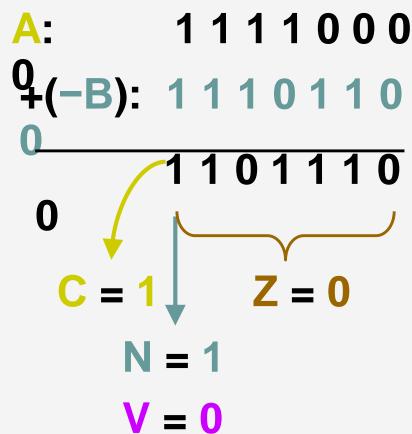

# **Condition Codes**

- The processor keeps track of information about the results of various operations.

- This is accomplished by recording the required information in individual bits, • called Condition Code Flags.

- Flags are grouped together in a special processor-register called the **condition** lacksquarecode register (or status register).

- 4 commonly used flags

- $\checkmark$  N (negative)

- $\checkmark$  Z (zero)

- $\checkmark$  V (overflow)

- ✓ C (carry)

10/19/2024TT201 / DP & CO / D.KAVITHA/AP/CSE(IoT) / Unit 3 / COMPUTER FUNDAMENTALS

## **Conditional Branch Instructions**

• Example:

- A: 11110000

- B: 00010100

10/19/2024

23ITT201 / DP & CO / D.KAVITHA/AP/CSE(IoT) / Unit 3 / COMPUTER FUNDAMENTALS

- 1111000

- 110

- $\mathbf{Z} = \mathbf{0}$

### Thank You

**10/19/2**024

23ITT201 / DP & CO / D.KAVITHA/AP/CSE(IoT) / Unit 3 / COMPUTER FUNDAMENTALS