# SNS COLLEGE OF ENGINEERING

Kurumbapalayam (PO), Coimbatore – 641 107

Accredited by NAAC-UGC with 'A' Grade

Approved by AICTE, Recognized by UGC & Affiliated to Anna University, Chennai

### DEPARTMENT OF INFORMATION TECHNOLOGY

**COURSE NAME: 23ITT201 DIGITAL PRINCIPLES AND**

**COMPUTER ORGANIZATION**

II YEAR/ III SEM

Unit 4: PROCESSOR

**Building a Data Path**

#### **BUILDING DATAPATH**

- Single-cycle Datapath: Each instruction executes in a single cycle

- Multi-cycle Datapath: Each instruction is broken up into a series of shorter steps

- Pipelined Datapath: Each instruction is broken up into a series of steps; Multiple instructions execute at once

# Differences between single cycle and multi cycle datapath

# **Single cycle Data Path:**

- o Each instruction is processed in one (long) clock cycle

- o Two separate memory units for instructions and data.

# **❖** Multi-cycle Data Path:

- o Divide the processing of each instruction into 5 stages and allocate one clock cycle per stage o Single memory unit for both instructions and data

- o Single ALU for all arithmetic operations

#### Creating a single cycle datapath

- ❖ This simplest datapath will attempt to execute all instructions in one clock cycle. This means that no datapath resource can be used more than once per instruction, so any element needed more than once must be duplicated.

- ❖ To share a datapath element between two different instruction classes, we may need to allow multiple connections to the input of an element, using a multiplexor and control signal to select among the multiple inputs.

- ❖ A reasonable way to start a datapath design is to examine the major components required to execute each class of MIPS instructions.

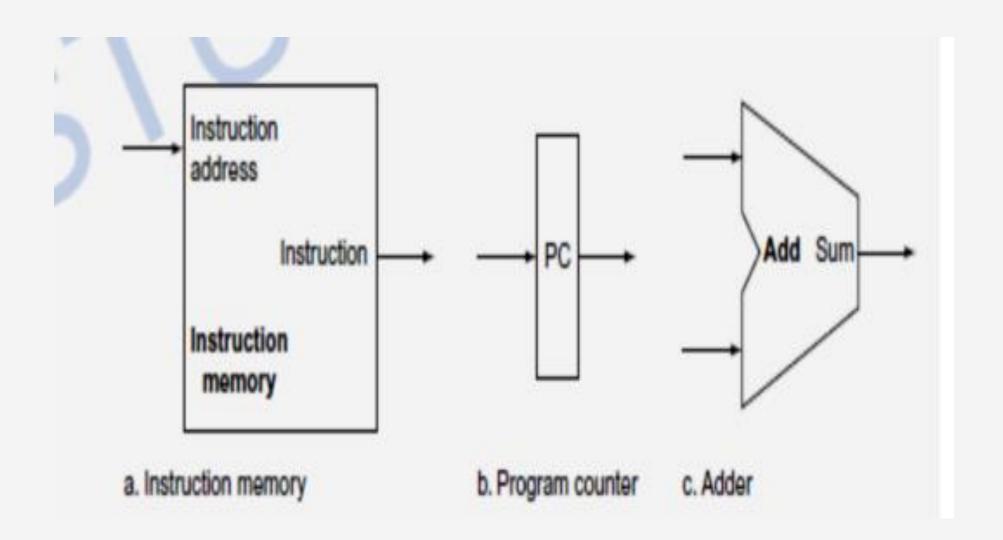

# **Datapath Element**

A unit used to operate on or hold data within a processor. In the MIPS implementation, the datapath elements include the instruction and data memories, the register file, the ALU, and adders.

# **Program Counter (PC)**

- The first element we need: a memory unit to store the instructions of a program and supply instructions given an address.

- Let also shows the program counter (PC), the register containing the address of the instruction in the program being executed.

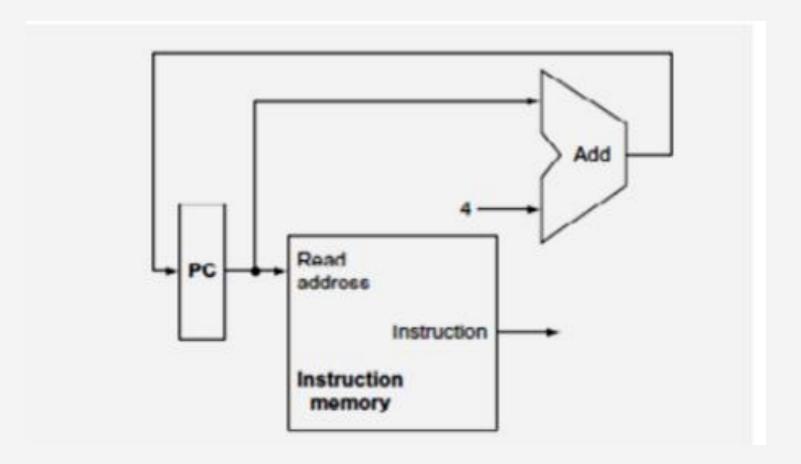

Two state elements are needed to store and access instructions, and an adder is needed to compute the next instruction address.

A portion of the datapath used for fetching instructions and incrementing the program counter. The fetched instruction is used by other parts of the datapath

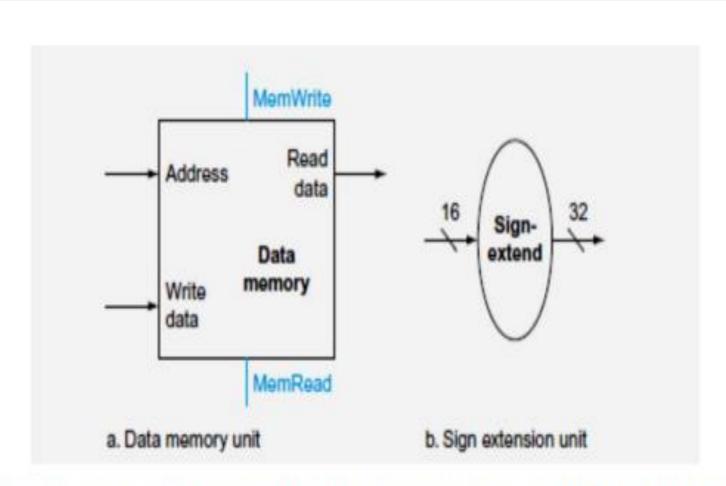

Fig 3.6: The two units needed to implement loads and stores, in addition to the register file and ALU of Figure 3.5

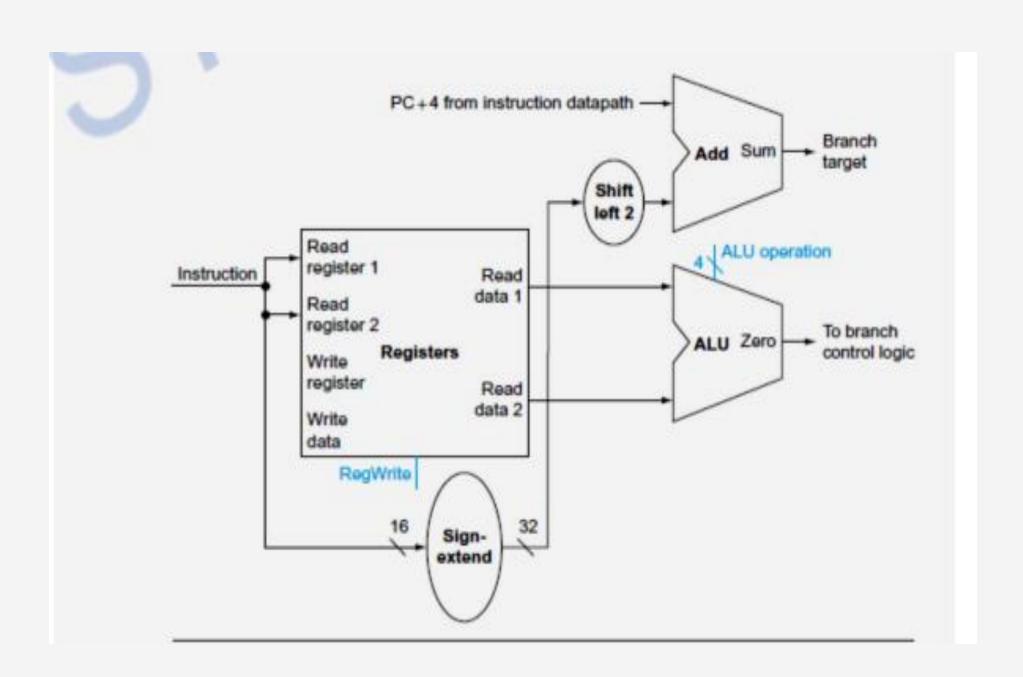

#### **DATAPATH SEGMENT FOR Branch INSTRUCTION**

# Thank You