# **SNS COLLEGE OF ENGINEERING**

Kurumbapalayam (Po), Coimbatore – 641 107

### **An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

### **DEPARTMENT OF ELECTRICAL AND ELECTRONICS** ENGINEERING

### **COURSE NAME : 23EET206 CONTROL SYSTEMS AND INSTRUMENTATION**

II YEAR ECE /III SEMESTER

### Unit 5-Oscilloscope, Signal Generator, Analyzer and Data **Acquisition System**

**Topic 3 : Frequency Synthesized Signal Generator**

Data Acquisition System/23EET206/Jebarani/EEE/SNSCE

**Redesigning Common Mind & Business Towards Excellence**

Build an Entrenreneurial Mindset Through Our Design Thinking FrameWou

# **FREQUENCY SYNTHESIZER**

A frequency synthesizer is an electronic circuit that generates a range of frequencies from a single reference frequency. devices such radio > Frequency synthesizers are used in as receivers, televisions, mobile telephones, radiotelephones, walkie-talkies, CB radios, cable television converter boxes, satellite receivers, and GPS systems.  $\succ$  A frequency synthesizer use the techniques of frequency may multiplication, frequency division, direct digital synthesis, frequency mixing, and phase-locked loops to generate its frequencies. The stability and accuracy of the frequency synthesizer's output are related to the stability and accuracy of its reference frequency input.

# **FREQUENCY SYNTHESIZER**

A **frequency synthesizer** can be of two types

- Direct Method (Direct Analog Synthesis or Direct Digital Synthesis)

- Indirect Method (Phase Locked Loop, Integer N Synthesizer and Fractional N Synthesizer)

**Redesigning Common Mind & Business Towards Excellence**

Build an Entrepreneurial Mindset Through Our Design Thinking FrameW

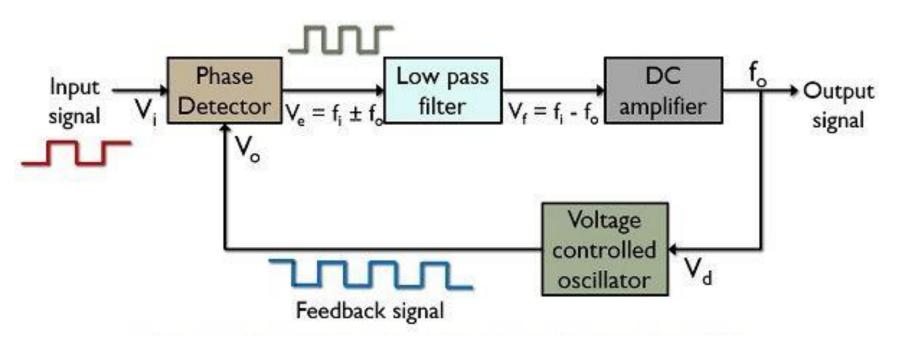

- A Phase-Locked Loop (PLL) is a negative feedback system consists of a phase detector, a low pass filter and a voltage controlled oscillator (VCO) within its loop.

Its purpose is to synchronize an output signal with a reference or input signal in frequency as well as in phase.

- In the synchronized or "locked" state, the phase error between the oscillator's output signal and the reference signal is zero, or it remains constant.

If a phase error builds up, a control mechanism acts on the oscillator to reduce the phase error to a minimum so that the phase of the output signal is actually locked

Redesigning Common Mind & Business Towards Excellence

Build an Entrepreneurial Mindset Through Our Design Thinking FrameWork

to the phase of the reference signal. This is why it is called a PLL.

The majority of PLL applications fall into four main categories:

- Frequency synthesis

- Frequency (FM) and phase (PM) modulation and demodulation.

- $\blacktriangleright$  Data and carrier recovery.

- Tracking filters.

**Classification of PLLs:**

- Analog or Linear PLL (LPLL), Digital PLL (DPLL) is Analog PLL with digital phase detector

- > All-Digital PLL (ADPLL) is a digital loop in two senses: all digital components and all digital (discrete-time) signals.

edesioning Common Mind & Rusiness Towards Excellence

The basic PLL block diagram consists of three components connected in a feedback loop :

### A Phase Detector (PD) or Phase Frequency Detector (PFD)

- produces a signal  $V_{\phi}$  proportional to the phase difference between the  $f_{in}$  and  $f_{osc}$  signal.

- A Loop Filter (LF)

- filters output voltage V<sub>out</sub> that controls the frequency of the VCO.

- A Voltage-Controlled Oscillator (VCO)

- V<sub>out</sub> at the input of the VCO determines the frequency f<sub>osc</sub> of the periodic signal V<sub>osc</sub> at the output of the VCO

A basic property of the PLL atemps to maintain the frequency lock  $f_{osc} = f_{in}$  between  $V_{osc}$  and  $V_{in}$  even if the frequency **f**<sub>in</sub> of the incoming signal varies in time. Assume the PLL is in the locked condition, and the frequency **f**<sub>in</sub> of the incoming signal increases slightly. The phase difference between the VCO signal and the incoming signal will begin to increase in time. As a result, the filtered output voltage V<sub>out</sub> increases I the VCO output frequency f<sub>osc</sub> increases until it matches f<sub>in</sub>, thus keeping the PLL in the locked condition. b

Redesioning Common Mind & Business Towards Excellence

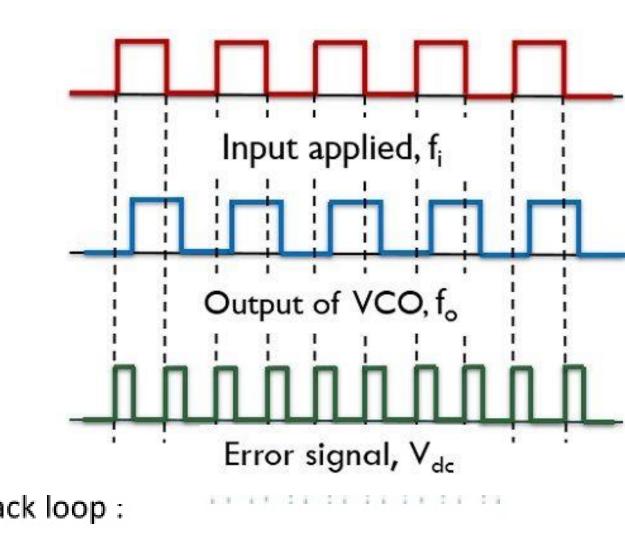

# **STAGES OF PLL**

There are three stages of PLL operations:

Free Running Stage: When no input is applied at the phase detector, PLL out put frequency is  $f_{osc} = f_o$ where fo free running frequency of the VCO.

Phase Locked Stage: Due to feedback mechanism, the frequency comparison stops when  $f_{osc} = f_{in}$ .

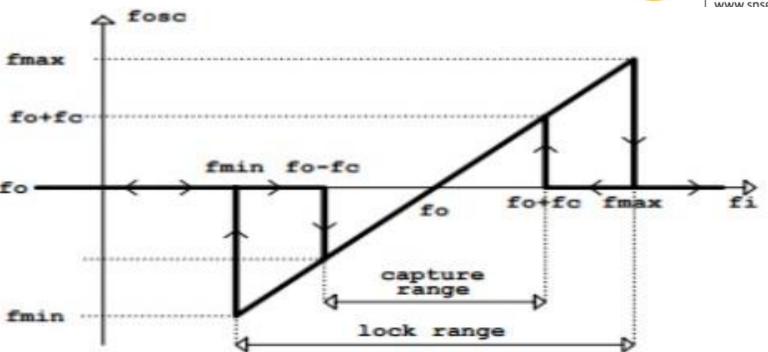

### Lock Range and Capture Range of PLL:

Lock Range of the PLL: The range of frequencies where the locked PLL remains in the locked:  $f_{min} \leq f_{in} \leq f_{max}$ The lock range is wider than the capture range.

- ٠

- If the PLL is initially locked, and if  $f_{max} < f_{in} < f_{min}$  the PLL becomes unlocked ( $f_{in} \neq f_{osc}$ ). When the PLL is unlocked, the  $f_{osc} = f_o$  where  $f_o$  is called the center frequency, or the free-running frequency of the VCO. ٠

**Capture Range of the PLL:** The lock can be established again if the incoming signal frequency **f**<sub>in</sub> gets close enough to **f**<sub>o</sub>. The range of frequencies such that the initially unlocked PLL becomes locked:  $f_0 - f_c \le f_{in} \le f_0 + f_c$ Sometimes a frequency detector is added to the phase detector to assist in initial acquisition of lock.

Redesigning Common Mind & Business Towards Excellence

Design Thinking FrameW

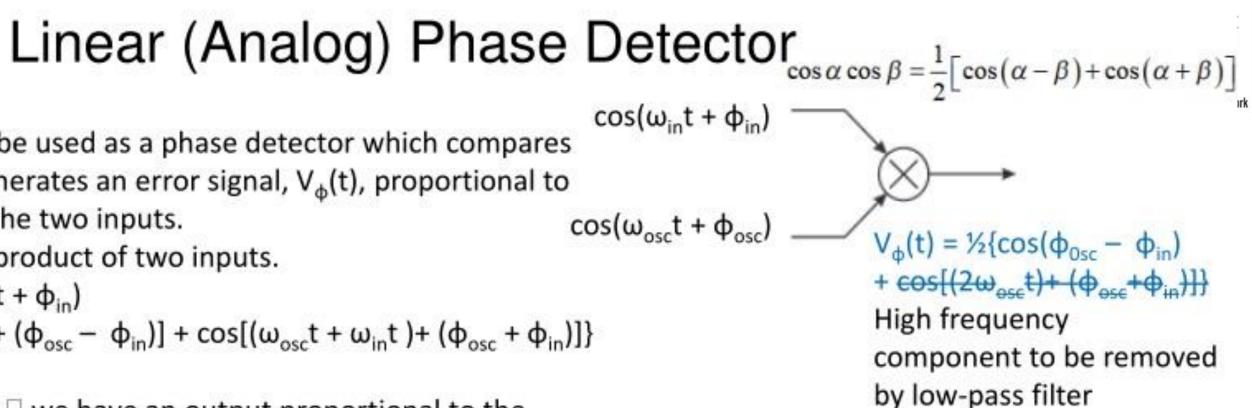

An analog multiplier mixer can be used as a phase detector which compares the phase at each input and generates an error signal,  $V_{\phi}(t)$ , proportional to the phase difference between the two inputs.

Recall that the mixer takes the product of two inputs.

$V_{\phi}(t) = \cos(\omega_{osc}t + \phi_{osc}) \cos(\omega_{in}t + \phi_{in})$

= (1/2) {cos[( $\omega_{osc}t - \omega_{in}t$ ) + ( $\varphi_{osc} - \varphi_{in}$ )] + cos[( $\omega_{osc}t + \omega_{in}t$ ) + ( $\varphi_{osc} + \varphi_{in}$ )]}

When loop is locked ( $\omega_{osc} = \omega_{in}$ )  $\Box$  we have an output proportional to the cosine of the phase difference and one output at twice the input frequency .  $V_{\phi}(t) = (1/2) \left\{ \cos(\phi_{osc} - \phi_{in}) + \cos[(2\omega_{osc}t) + (\phi_{osc} + \phi_{in})] \right\}$

The doubled frequency component will be removed by the low-pass loop filter. Any phase difference then shows up as the control voltage to the VCO, a DC or slowly varying AC signal after filtering. K<sub>D</sub> is the gain of the phase detector (V/rad).

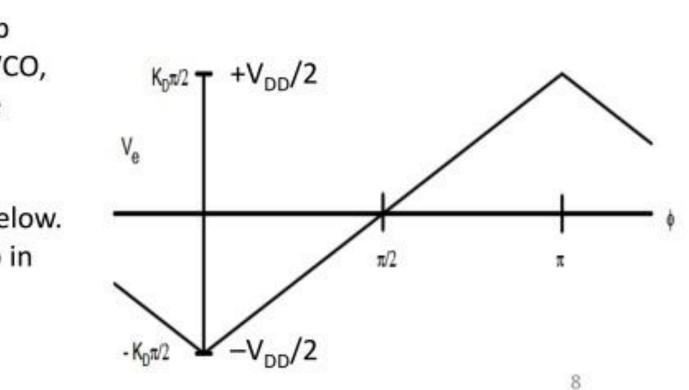

$V_{\phi}(t) = K_{p} (\phi_{osc} - \phi_{in})$  where  $K_{p} \pi/2 = V_{pp}/2 \Box K_{p} = V_{pp}/\pi$ The averaged transfer characteristic of such a phase detector is shown below. Note that in many implementations, the characteristic may be shifted up in voltage (single supply/single ended).

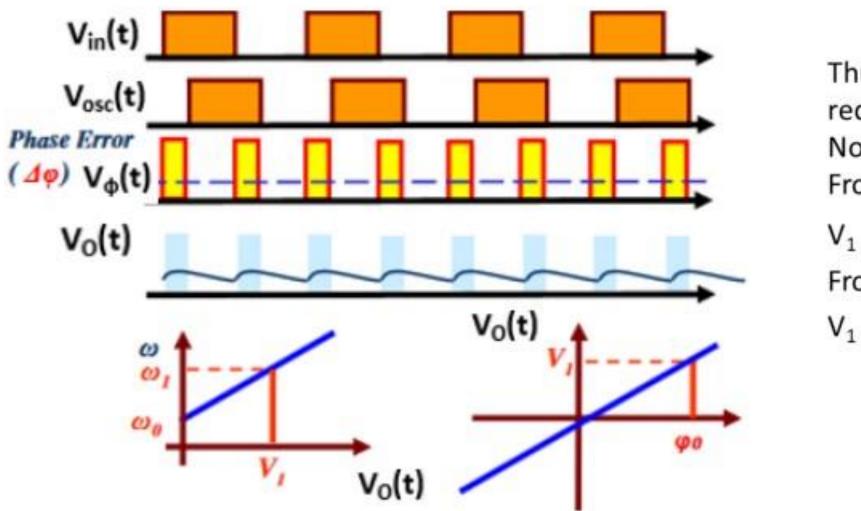

# Digital Phase Detector

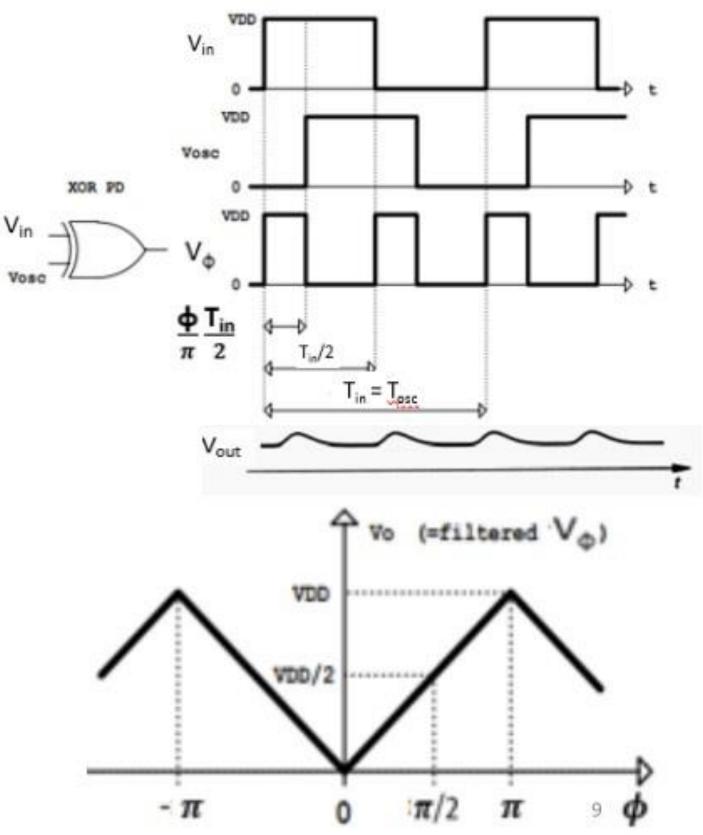

A simple digital phase detector is an XOR gate with logic low output ( $V_{\phi} = 0V$ ) and the logic high output ( $V_{\phi} = V_{DD}$ ). An example below shows the PLL is in the locked condition where V<sub>in</sub> and V<sub>osc</sub> are two phase-shifted periodic square-wave signals at the same frequency  $f_{osc} = f_{in} = \frac{1}{T_{in}}$ , and with 50% duty ratios. The output of the phase detector is a periodic square-wave signal  $V_{\phi}(t)$  at the frequency  $2f_{in}$ , and with the duty ratio  $D_{\phi}$  that depends on the phase difference  $\phi(t) = [\phi_{osc}(t) - \phi_{in}(t)]$  between  $V_{in} \text{ and } V_{osc} \rightarrow D_{\phi} = \frac{\Phi}{\pi}$  (for XOR)

The dc component  $V_{\varphi}$  of the phase detector output can be found easily as the average of  $V_{\phi}(t)$  over a period  $\frac{T_{in}}{2}$

$\Rightarrow$  V<sub> $\phi$ </sub> =  $\frac{V_{DD}}{\pi} \phi = K_D \phi$  K<sub>D</sub> is called PD gain (for XOR) where  $K_D = \frac{V_{DD}}{\pi} \text{ volt/rad}$  for  $0 \le \phi \le \pi$ The average output rise to  $V_{out} = \frac{V_{DD}}{\pi} \Delta \Phi = 0 \rightarrow VDD$  when  $\Delta \Phi$ goes from  $0 \rightarrow \pi$ . For  $\Delta \Phi > \pi$ , the average output begins to drop.

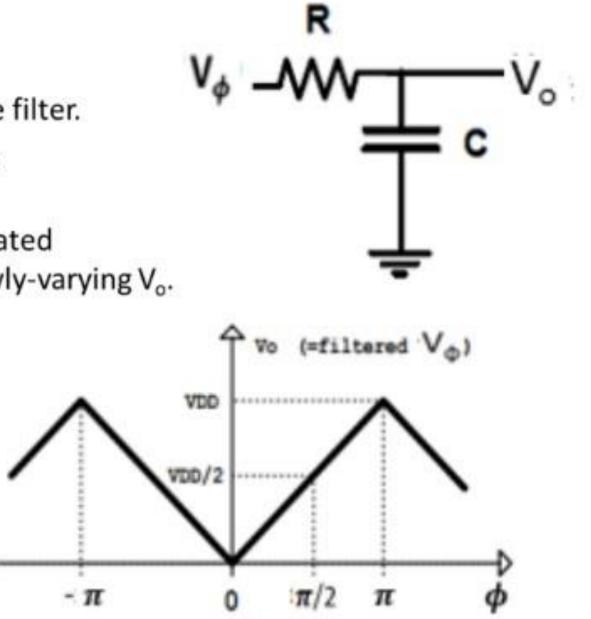

# Loop Filter

The output V<sub>b</sub>(t) of the phase detector is filtered by the low-pass loop filter. The purpose of the low-pass filter is to pass the dc and low-frequency portions of  $V_{\phi}(t)$  and to attenuate high-frequency ac components at frequencies  $2\pi f_{in}$ . The simple RC filter has the transfer function:

$$F(s) = \frac{1}{1+s R C} = \frac{1}{1+s/\omega_p}$$

where  $\omega_p = \frac{1}{R C}$  and  $f_p = \frac{\omega_p}{2\pi}$  is the cut-off frequency of the

If  $f_p << 2f_{in} \rightarrow$  the output of the filter  $V_{out}$  is approximately equal to the dc component  $V_{\phi}$  of the phase detector output.

In practice, the high-frequency components are not completely eliminated and can be observed as high-frequency ac ripple around the dc or slowly-varying V<sub>o</sub>.

In general, the filter output V<sub>out</sub> as a function of the phase difference. Note that  $V_{out} = 0$  if  $V_{in}$  and  $V_{osc}$  are in phase ( $\phi = 0$ ), and that it reaches the maximum value  $V_{out} = V_{DD}$  when the two signals are exactly out of phase ( $\phi = \pi$ ).

For  $0 \le \phi \le \pi$ , V<sub>o</sub> increases, and for  $\phi > \pi$ , V<sub>o</sub> decreases. The characteristic of periodic in  $\phi$  with period  $2\pi$ .

The range  $0 \le \phi \le \pi$  is the range where the PLL can operate in the locked condition.

# Voltage Controlled Oscillator (VCO)

In PLL applications, the VCO is treated as a linear, time-invariant system. To obtain an arbitrary output frequency (within the VCO tuning range), a finite V<sub>out</sub> is required. Let's define  $\phi_{osc} - \phi_{in} = \phi_{o}$ . The XOR function produces an output pulse whenever there is a phase misalignment. Suppose that an output frequency  $\omega_1$  is needed. From the upper right figure, we see that a control voltage V<sub>1</sub> will be necessary to produce this output frequency. The phase detector can produce this V<sub>1</sub> only by maintaining a phase offset φ at its input. In order to minimize

the required phase offset or error, the PLL loop gain,  $K_D K_O$ , should be maximized, since  $\phi =$

Thus, a high loop gain K<sub>p</sub>K<sub>o</sub> is beneficial for reducing phase errors. Note:

From Phase detector:

$$\sum_{I} = K_{D} \phi \Rightarrow \phi = \frac{V_{1}}{K_{D}}$$

from VCO:

$$\sum_{I} = \frac{\omega_{1} - \omega_{0}}{K_{D}} \Rightarrow \phi = \frac{V_{1}}{K_{D}} = \frac{\omega_{1} - \omega_{0}}{K_{D}K_{D}}$$

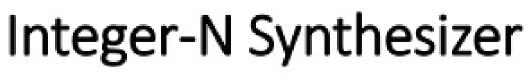

- The resolution of the output frequency is determined by the reference frequency applied to the phase detector. Step size or frequency resolution - the smallest frequency increment possible.

- To obtain a stable low frequency source is not easy, because a quartz crystal oscillating in kHz region is quite bulky ٠ and not practical. A sensible approach is to take a good stable crystal-based high frequency source and an integer-N synthesizer to divide it down.

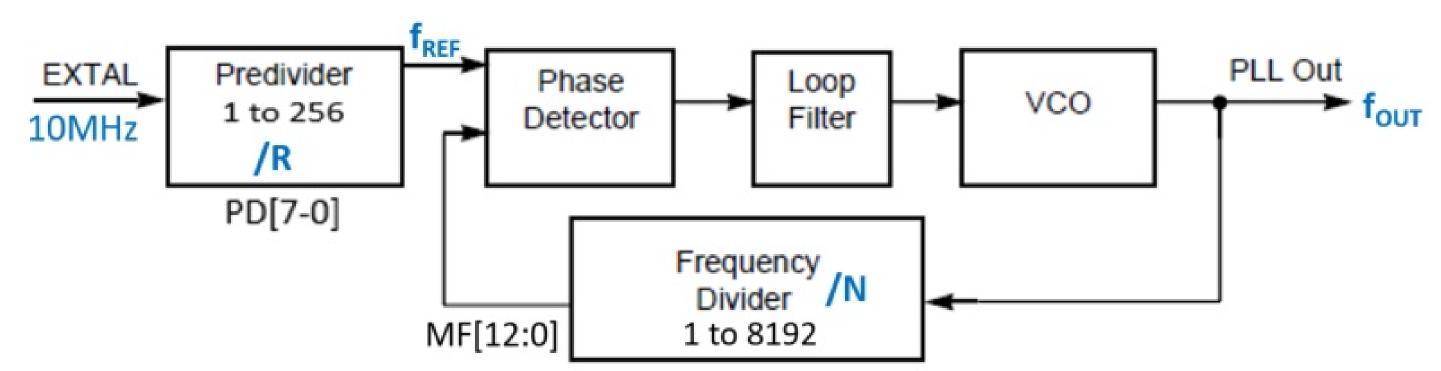

## **Fractional-N Synthesizer**

Fractional-N allows the resolution at the PLL output to be reduced to small fractions of the PFD frequency as shown below, where the PFD input frequency is 1 MHz. It is possible to generate output frequencies with resolutions of 100s of Hz, while maintaining a high PFD frequency. As a result the N-value is significantly less than for integer-N.

# References

Albert D. Helfrick, William D. Cooper, "Modern Electronic Instrumentation and Measurement Techniques", Pearson, 1<sup>st</sup> Edition, 2016 (Unit IV-V).

Sawhney A K., "Course in Electrical, Electronic Measurements and Instrumentation", Shree Hari Publications, 2021(Unit IV-V).

Patranabis D, "Principles of Industrial Instrumentation", Mc-Graw Hill Education, 3<sup>rd</sup> Edition, 2017 (Unit IV-V).

# **Thank You**

Redesigning Common Mind & Business Towards Excellence

Build an Entrepreneurial Mindset Through Our Design Thinking FrameWork