## SNS COLLEGE OF ENGINEERING

Kurumbapalayam (PO), Coimbatore – 641 107

#### **An Autonomous Institution**

Accredited by NAAC – UGC with 'A' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

#### SYNCHRONOUS UP COUNTERS

Dr.G.Arthy

Assistant Professor

Department of EEE

SNS College of Engineering

## **SYNCHRONOUS UP COUNTERS**

- ✓ A counter is a device which can count any particular event on the basis of how many times the particular event(s) is occurred.

- ✓ Counters are implemented using Flipflops.

- ✓ In synchronous counter, the clock input across all the flip-flops use the same source and create the same clock signal at the same time. So, a counter which is using the same clock signal from the same source at the same time is called Synchronous counter.

#### SYNCHRONOUS UP COUNTERS

#### **APPLICATIONS**

- ✓ Machine Motion control

- ✓ Motor RPM counter

- ✓ Rotary Shaft Encoders

- ✓ Digital clock or pulse generators.

- ✓ Digital Watch and Alarm systems.

#### **DESIGN PROCEDURE**

- ✓ **Step 1:** Select the required number of flipflops and the type of flipflops.

- ✓ **Step 2:** Draw the excitation table for the Flipflop.

- ✓ Step 3: Draw the state diagram.

- ✓ **Step 4:** Draw the excitation table for the logic diagram.

- ✓ **Step 5:** Draw K Map to find the minimal Boolean expression.

- ✓ **Step 6:** Draw the logic diagram for the up counter.

#### **Problem Statement**

Design a Synchronous 3 bit Up Counter

# Step 1 :Select the required number of flipflops and the type of flipflops.

- Let us consider JK Flip Flop

- Since it is a 3 bit counter we need 3 flip flops.

## Step 2: Draw the excitation table for the Flipflop.

| <b>Q</b> <sub>n</sub> | Q <sub>n+1</sub> | J | K |  |

|-----------------------|------------------|---|---|--|

| 0                     | 0                | 0 | Х |  |

| 0                     | 1                | 1 | 0 |  |

| 1                     | 0                | Χ | 1 |  |

| 1                     | 1                | X | 0 |  |

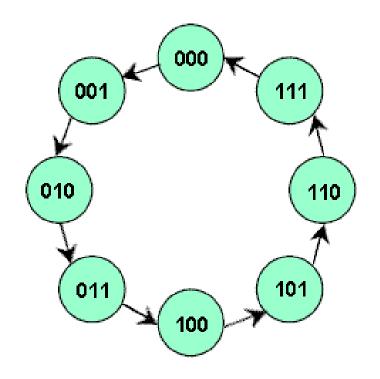

# Step 3: Draw the state diagram

# Step 4: Draw the excitation table for the logic diagram

| Clock | Present State |    |         | Next State       |      | Flip flop Inputs |                |    |                |   |    |   |

|-------|---------------|----|---------|------------------|------|------------------|----------------|----|----------------|---|----|---|

|       | Qc            | Qn | $Q_{A}$ | Q <sub>C+s</sub> | Q.,, | Q                | J <sub>c</sub> | Kc | J <sub>E</sub> | K | JA | K |

| 1     | 0             | 0  | 0       | 0                | 0    | 1                | 0              | x  | 0              | x | 1  | x |

| 2     | 0             | 0  | 1       | 0                | 1    | 0                | 0              | x  | 1              | x | х  | 1 |

| 3     | 0             | 1  | 0       | 0                | 1    | 1                | 0              | x  | x              | 0 | 1  | x |

| 4     | 0             | 1  | 1       | 1                | 0    | 0                | 1              | x  | x              | 1 | X  | 1 |

| 5     | 1             | 0  | 0       | 1                | 0    | 1                | x              | 0  | 0              | x | 1  | x |

| 6     | 1             | 0  | 1       | 1                | 1    | 0                | X              | 0  | 1              | x | x  | 1 |

| 7     | 1             | þ  | 0       | 1                | 1    | 1                | x              | 0  | x              | 0 | 1  | x |

| 8     | 1             | 1  | 1       | 0                | 0    | 0                | x              | 1  | x              | 1 | x  | 1 |

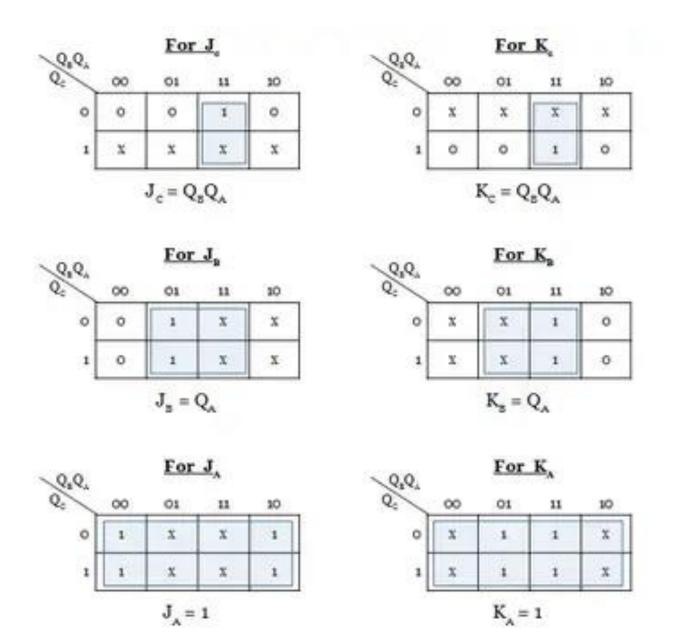

## Step 5: Draw K Map to find the minimal Boolean expression.

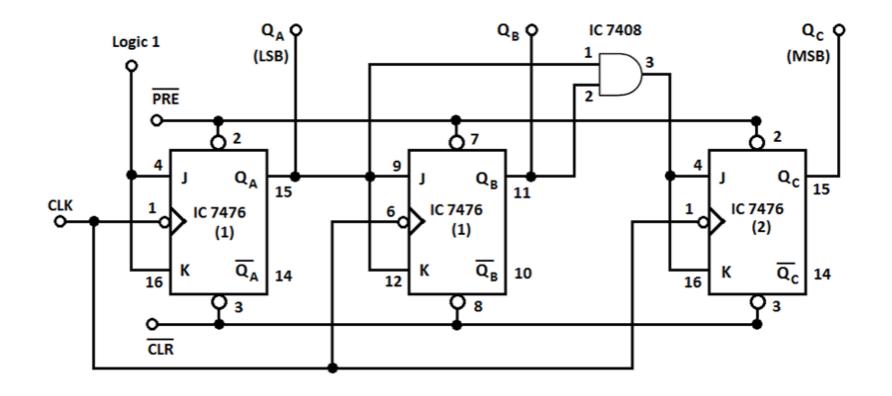

# Step 6: Draw the logic diagram for the up counter.

| J <sub>A</sub> = 1            | $K_A = 1$       |  |  |  |

|-------------------------------|-----------------|--|--|--|

| $\mathbf{J_B} = \mathbf{Q_A}$ | $K_B = Q_A$     |  |  |  |

| $J_c = Q_g Q_A$               | $K_c = Q_s Q_A$ |  |  |  |

#### **Assessment**

1. How many Flipflops are required to design a 4 bit Counter?

2. How many states will be there for a 3 bit counter?