### SNS COLLEGE OF ENGINEERING

Kurumbapalayam (Po), Coimbatore – 641 107

#### **An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### DEPARTMENT OF COMPUTER SCIENCE AND DESIGN

# COURSE NAME: 19EE01 BASIC ELECTRICAL AND ELECTRONICS ENGINEERING

I YEAR /II SEMESTER - COMPUTER SCIENCE AND DESIGN

Topic 7 : Full Adders

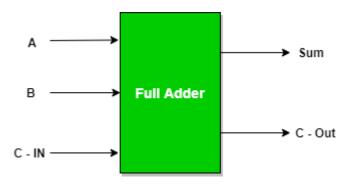

#### Full Adder

Full Adder is the adder that adds three inputs and produces two outputs. The first two inputs are A and B and the third input is an input carry as C-IN. The output carry is designated as C-OUT and the normal output is designated as S which is SUM. The C-OUT is also known as the majority 1's detector, whose output goes high when more than one input is high. A full adder logic is designed in such a manner that can take eight inputs together to create a byte-wide adder and cascade the carry bit from one adder to another. we use a full adder because when a carry-in bit is available, another 1-bit adder must be used since a 1-bit half-adder does not take a carry-in bit. A 1-bit full adder adds three operands and generates 2-bit results.

#### **Adder Truth Table:**

| inputs |   |      | Outputs |       |

|--------|---|------|---------|-------|

| A      | В | C-IN | Sum     | C-Out |

| 0      | 0 | 0    | 0       | 0     |

| 0      | 0 | 1    | 1       | 0     |

| 0      | 1 | 0    | 1       | 0     |

| 0      | 1 | 1    | 0       | 1     |

| 1      | 0 | 0    | 1       | 0     |

| 1      | 0 | 1    | 0       | 1     |

| 1      | 1 | 0    | 0       | 1     |

| 1      | 1 | 1    | 1       | 1     |

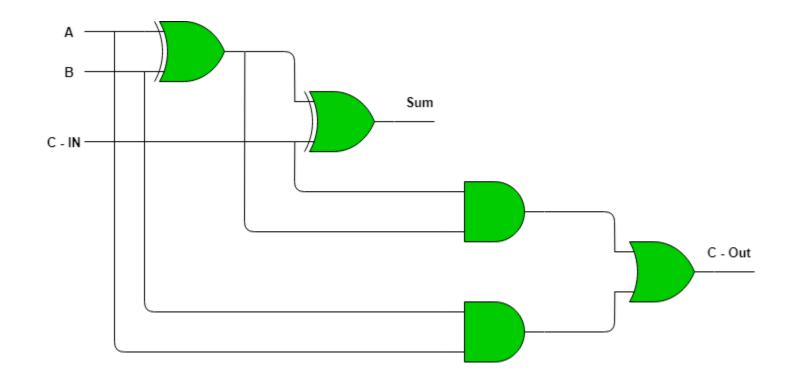

**Logical Expression for SUM:** = A' B' C-IN + A' B C-IN' + A B' C-IN' + A B C-IN = C-IN (A' B' + A B) + C-IN' (A' B + A B') = C-IN XOR (A XOR B) = (1,2,4,7)

**Logical Expression for C-OUT:** = A' B C-IN + A B' C-IN + A B C-IN' + A B C-IN = A B + B C-IN + A C-IN = (3,5,6,7)

Another form in which C-OUT can be implemented: = A B + A C-IN + B C-IN (A + A') = A B C-IN + A B + A C-IN + A' B C-IN = A B (1 + C-IN) + A C-IN + A' B C-IN = A B + A C-IN + A' B C-IN = A B C-IN + A B + A B' C-IN + A' B C-IN = A B C-IN (A' B + A B')

Therefore COUT = AB + C-IN (A EX - OR B)

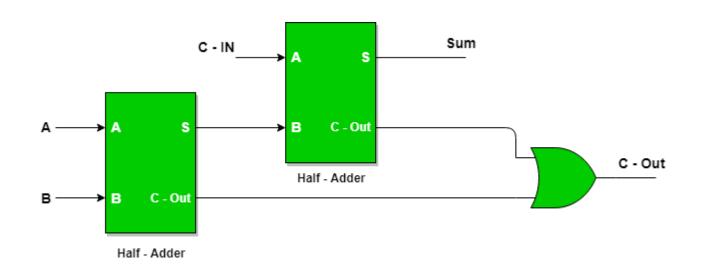

#### **Implementation of Full Adder using Half Adders:**

2 Half Adders and an OR gate is required to implement a Full Adder.

With this logic circuit, two bits can be added together, taking a carry from the next lower order of magnitude, and sending a carry to the next higher order of magnitude.

## Any Query????

Thank you.....